# DCB1M - UART/SPI/I<sup>2</sup>C Over Powerline Transceiver

### 1. Overview

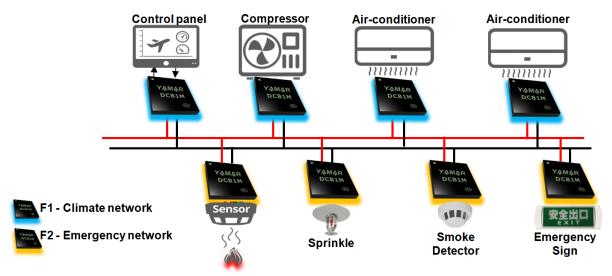

The DCB1M is a device for multiplex communication over noisy power lines, at speed up to 1.4Mbit/s. The DCB1M is based on the DC-BUS™ technology for network communication between modules sharing a common DC or AC powerline. The device avoids complex cabling, saves weight, and simplifies installation. The DCB1M supports UART, SPI, and I²C protocols, enabling the user to meet this application protocol. Sleep mode allows low power consumption when the device is not used. A QFN32 5x5 mm package provides a small PCB footprint ★ The DCB1M is beneficial for many applications ranging from Aerospace, Automotive, Industrial, and even Toys.

### **Applications**

- Battery management (BMS)

- Climate control network

- Sensors/actuators bus

- Robotics control network

- Lighting control

- Truck-Trailer communication

- Multiple vehicle networks sharing the same powerline

### **Features**

- Noise robust UART, SPI, and I<sup>2</sup>C transceiver over DC powerline.

- Bitrate up to 1.4Mbit/s over the powerline.

- Multiple networks may operate over a single powerline.

- 251 selectable carrier frequencies (5MHz to 30MHz).

- Built-in CSMA/CA (powerline arbitration) mechanism.

- Operates as Multi-master Transceiver in a multiplex network.

- Channel interference detection.

- Communicates over a wide range of DC voltages.

- Power management (Sleep modes) for low power consumption.

Figure 1 - DCB1M climate control and security networks sharing single powerline

# **Table of Content**

| 1.  | OVERVIEW                                                                               |

|-----|----------------------------------------------------------------------------------------|

| 2.  | DESCRIPTION                                                                            |

| 2.1 | The DCB1M network5                                                                     |

| 2.2 | DCB1M channel parameters5                                                              |

| 2.3 | Device architecture                                                                    |

| 2.4 | Pin configuration and function 6                                                       |

| 2.5 | Implementation8                                                                        |

| 3.  | DCB1M OPERATION11                                                                      |

| 3.1 | DCB1M messages                                                                         |

| 3.2 | Device configuration                                                                   |

| 3.3 | Carrier frequency configuration14                                                      |

| 3.4 | <i>TX-Trigger</i> mode                                                                 |

| 3.5 | Carrier Sense mode (CS)16                                                              |

| 3.6 | Arbitration mode (ARB)16                                                               |

| 3.7 | DCB1M UUID16                                                                           |

| 4.  | POWER OPERATION MODES                                                                  |

| 4.1 | Normal mode                                                                            |

| 4.2 | Standby mode                                                                           |

| 4.3 | Sleep modes (power-saving)17                                                           |

| 5.  | DCB1M REGISTERS21                                                                      |

| 5.1 | REG_0 - 'Device Control 0' (Address 0x00)21                                            |

| 5.2 | REG_1 - 'Device Control 1' (Address 0x01)21                                            |

| 5.3 | REG_2 - 'Frequency Select' (Address 0x02)22                                            |

| 5.4 | REG_3 - 'Sleep & IO Control' (Address 0x03)22                                          |

| 5.5 | REG_4 - 'Interrupts Enable (Address 0x04) (SPI & I <sup>2</sup> C Only)22              |

| 5.6 | REG_5 - 'Interrupt RX-FIFO Threshold 1' (Address 0x05) (SPI & I <sup>2</sup> C Only)22 |

| 5.7 | REG_6 - 'Interrupt RX-FIFO Threshold 2' and Error status (Address 0x06)22              |

| 5.8  | Status interrupt byte (Accessed only in SPI& I <sup>2</sup> C, through READ-INT command) | 23 |

|------|------------------------------------------------------------------------------------------|----|

| 5.9  | REG_3C - 'Interrupt TX-FIFO Thresholds1' (Address 0x3C) (SPI & I <sup>2</sup> C Only)    | 23 |

| 5.10 | REG_3D - 'Interrupt TX-FIFO Thresholds2' (Address 0x3D) (SPI & I <sup>2</sup> C Only)    | 23 |

| 5.11 | REG_3E - 'Interrupt TX-FIFO Thresholds 3' (Address 0x3E) (SPI & I <sup>2</sup> C Only)   | 23 |

| 5.12 | REG_7 - 'Arbitration ID 1' (Address 0x07)                                                | 23 |

| 5.13 | REG_8 - 'Arbitration ID 2' (Address 0x08)                                                | 23 |

| 5.14 | REG_59 – UUID[47:40] (Address 0x59)                                                      | 24 |

| 5.15 | REG_5A – UUID[39:32] (Address 0x5A)                                                      | 24 |

| 5.16 | REG_5B – UUID[31:24] (Address 0x5B)                                                      | 24 |

| 5.17 | REG_5C – UUID[23:16] (Address 0x5C)                                                      | 24 |

| 5.18 | REG_5D - UUID[15:8] (Address 0x5D)                                                       | 24 |

| 5.19 | REG_5E – UUID[7:0] (Address 0x5E)                                                        | 24 |

| 6. U | JART PROTOCOL INTERFACE                                                                  | 24 |

| 6.1  | Interfacing to UART ECU                                                                  | 24 |

| 6.2  | UART registers configuration (Command mode)                                              | 25 |

| 6.3  | UART Bitrate configuration (Bitrate learning)                                            | 25 |

| 6.4  | UART Codec Select configuration                                                          | 26 |

| 6.5  | UART RTR pin handling                                                                    | 26 |

| 6.6  | UART interface typical set-up and operation                                              | 26 |

| 6.7  | UART Examples                                                                            | 26 |

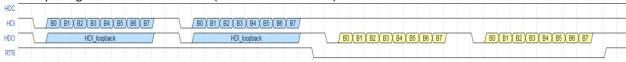

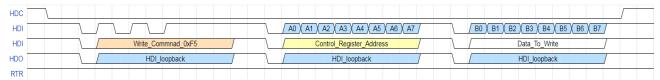

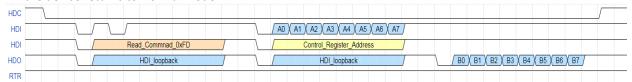

| 7. S | PI PROTOCOL INTERFACE                                                                    | 28 |

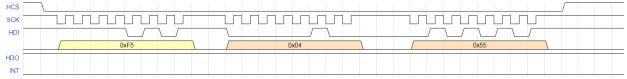

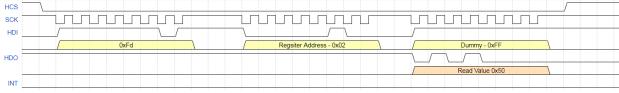

| 7.1  | Interfacing to SPI ECU                                                                   | 28 |

| 7.2  | SPI Flow control                                                                         | 28 |

| 7.3  | SPI Message (frame) construction                                                         | 28 |

| 7.4  | SPI Status interrupt byte                                                                | 28 |

| 7.5  | SPI Commands                                                                             | 29 |

| 7.6  | SPI interface typical set-up and operation                                               | 31 |

| 7.7  | SPI Examples                                                                             |    |

|      |                                                                                          |    |

| 8.   | I <sup>2</sup> C PROTOCOL INTERFACE                       | 34 |

|------|-----------------------------------------------------------|----|

| 8.1  | Interfacing to I <sup>2</sup> C ECU                       | 34 |

| 8.2  | 2 I <sup>2</sup> C Flow control                           | 34 |

| 8.3  | B I <sup>2</sup> C Status interrupt byte                  | 34 |

| 8.4  | I <sup>2</sup> C Message (frame) construction             | 35 |

| 8.5  | 5 I <sup>2</sup> C Commands                               | 35 |

| 8.6  | 5 I <sup>2</sup> C interface typical set-up and operation | 38 |

| 8.7  | <sup>7</sup> I <sup>2</sup> C Examples                    | 38 |

| 9.   | SPECIFICATIONS                                            | 40 |

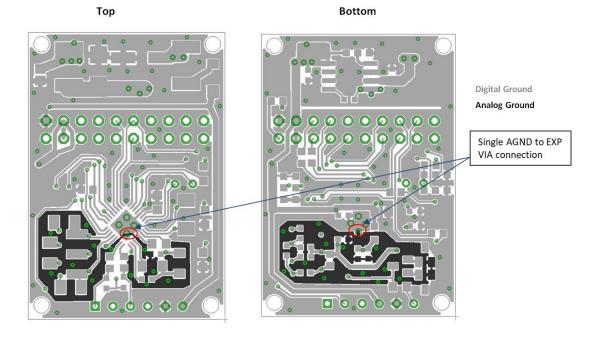

| 10.  | . DCB1M PCB LAYOUT RECOMMENDATION                         | 42 |

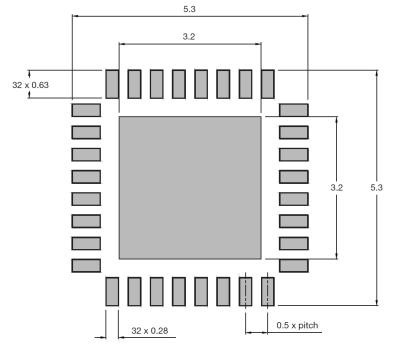

| 11.  | . PACKAGE, MECHANICAL                                     | 44 |

| 11.1 | .1 Mechanical Drawing                                     | 44 |

| 11.2 | .2 PCB drawing                                            | 44 |

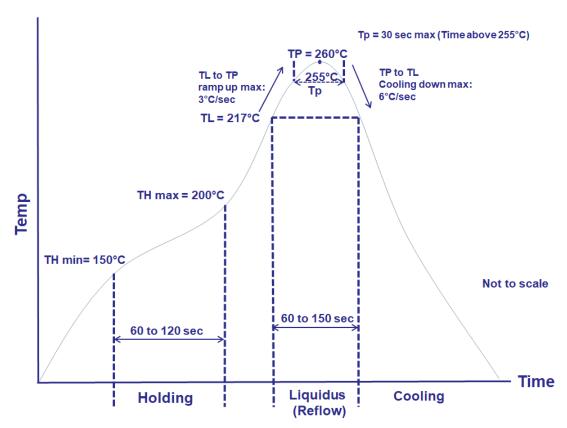

| 11.3 | .3 Soldering profile                                      | 44 |

#### 2. Description

#### The DCB1M network 2.1

The DCB1M operates as part of a powerline (DC-BUS) communication network consisting of multiple DCB1M devices. Each device can transmit messages (frames) to other devices over the power lines at four selectable coding strengths and bitrates, ranging from 1.4Mbit/s down to 225Kbit/s for a very noisy channel. The data is phase modulated by a sine wave at a user predefined carrier frequency.

Each DCB1M can communicate with its host controller (ECU) using one of the supported protocols (UART, SPI, and I<sup>2</sup>C). One ECU using SPI protocol interface can communicate with another ECU interfacing with UART or I<sup>2</sup>C protocol and vice versa. The DCB1M operates as a gateway between the ECUs' different protocols.

All network topologies (e.g. Star, ring, line, tree, etc.) are applicable, as long as the RX signal level at RXI is above minimal RXI<sub>lev</sub> (see Table 35).

Users may create multiple DCB1M networks operating over a single powerline, where each network communicates using a different carrier frequency (channel).

#### 2.2 DCB1M channel parameters

Carrier frequency: 251 selectable frequencies between 5MHz - 30MHz with 100 kHz spacing.

Powerline bitrate: 1.4Mbit/s, 1Mbit/s, 490Kbit/s, 225Kbit/s

Any, with proper powerline coupling interfacing (see 2.5.6) Powerline voltage:

Cable length: Depends on the powerline loads AC signal-attenuation (100m is practicable)

Cable type: Any cable.

#### Device architecture 2.3

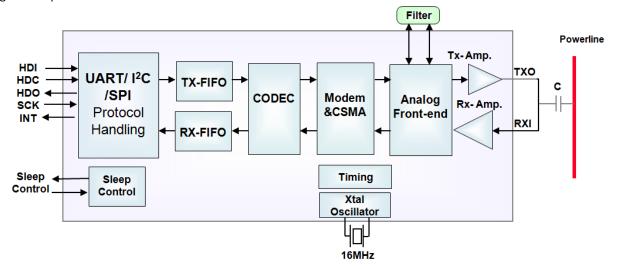

Figure 2 depicts the DCB1M blocks.

Figure 2 - DCB1M block diagram

The DCB1M main building blocks:

- Protocol handling Interprets the ECU protocol.

- Transmit and Receive FIFOs allows 2 x 1024 bytes data buffering between the ECU and the DCB1M.

- **CODEC** Encodes/decodes the data according to the selected channel protection code (bitrate).

- Modem Phase modulates and demodulates the data to and from the DC-BUS powerline.

- **CSMA/CA** Allows Carrier sense and arbitration capabilities to the device

- Sleep Ensures low power consumption during Sleep mode.

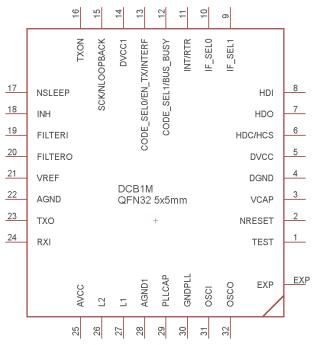

#### 2.4 Pin configuration and function

#### 2.4.1 Pinout diagram

Figure 3 - DCB1M pinout diagram in QFN32 5x5mm package

#### 2.4.2 **Signals and Pinout description**

Table 1 - Pinout description

| Table 1 - Fillout description |       |                |                        |                                                            |                                                          |  |  |

|-------------------------------|-------|----------------|------------------------|------------------------------------------------------------|----------------------------------------------------------|--|--|

|                               |       |                | Internal               |                                                            |                                                          |  |  |

| Name                          | Pin # | Pin type       | PU/PD                  | Description                                                |                                                          |  |  |

|                               |       |                |                        | Digital IO signal. In SPI and UART interfaces, Outputs the |                                                          |  |  |

|                               |       |                | PU                     |                                                            | n the powerline or from internal registers               |  |  |

|                               |       | Digital IO     | (SPI, I <sup>2</sup> C | to the ECU. In the                                         | I <sup>2</sup> C interface, this pin is IO and should be |  |  |

| HDO                           | 7     | 12mA           | Only)                  | externally pull-up v                                       | with a $10$ k $\Omega$ resistor.                         |  |  |

|                               |       |                |                        | Digital data input                                         | signal. Transfers data from the ECU to the               |  |  |

| HDI                           | 8     | Digital input  | PU                     | powerline or the in                                        | iternal registers.                                       |  |  |

|                               |       |                |                        | UART - ECU data /                                          | / command input, enables read and write                  |  |  |

| HDC                           |       |                |                        | from/to DCB1M co                                           | ntrol registers (see section 6.2)                        |  |  |

| /HCS                          | 6     | Digital input  | PU                     | SPI - Chip Select in                                       | put.                                                     |  |  |

| TEST                          | 1     | Digital Input  | PD                     | Should be connected                                        | ed to GND.                                               |  |  |

| NRESET                        | 2     | Digital Input  | PU                     | Reset, active low.                                         |                                                          |  |  |

|                               |       |                |                        | Sleep mode contro                                          | l input (see section 4.3).                               |  |  |

| NSLEEP                        | 17    | Digital Input  |                        | Should be pull-up t                                        | to 3.3V when not in use.                                 |  |  |

|                               |       |                |                        | ECU interface selec                                        | ction inputs.                                            |  |  |

|                               |       |                |                        | IF_SEL[1:0]                                                | Interface                                                |  |  |

|                               |       |                |                        | '00'                                                       | UART                                                     |  |  |

|                               |       |                |                        | '01'                                                       | Not Valid                                                |  |  |

| IF_SEL1                       | 9     | Digital Input  |                        | '10'                                                       | SPI                                                      |  |  |

| IF_SEL0                       | 10    | Digital Input  |                        | '11'                                                       | I <sup>2</sup> C                                         |  |  |

|                               |       |                |                        | SPI/I <sup>2</sup> C - Interrupt                           | event indication. See section 7.4 and 8.3).              |  |  |

|                               |       |                |                        | <b>UART-RTR</b> (Ready                                     | to Receive). When high, ECU can transfer                 |  |  |

|                               |       | Digital Output |                        | bytes through the HDI pin. When low, ECU should pause its  |                                                          |  |  |

| INT/RTR                       | 11    | 8mA            |                        | data bytes transfer.                                       |                                                          |  |  |

|                               |       |                |                        | SPI/ I <sup>2</sup> C - Serial Clock Input.                |                                                          |  |  |

| SCK                           |       |                | PU                     | UART- NLOOPBACK, when high, loopback from HDO to HDI is    |                                                          |  |  |

| /NLOOPBACK                    | 15    | Digital Input  | (UART only)            | disabled.                                                  |                                                          |  |  |

| Name                   | Pin # | Pin type                  | Internal<br>PU/PD |                                                              |                                              | Descriptio         | n                        |       |

|------------------------|-------|---------------------------|-------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|--------------------------|-------|

| Nume                   | 1 #   | Digital Output            | 10/10             | When high, DCB1M is in Normal mode                           |                                              |                    |                          |       |

| INH                    | 18    | 8mA                       |                   | When low, DCB1M is in Sleep mode                             |                                              |                    |                          |       |

|                        |       |                           |                   | UART                                                         |                                              | ·                  |                          |       |

|                        |       |                           |                   | REG_3                                                        | [5:4]                                        | Pin Function       | Pin Type                 |       |

|                        |       |                           |                   | '00' (D                                                      | efault)                                      | CODE_SEL0          | Input                    |       |

|                        |       |                           |                   | '01'                                                         |                                              | EN_TX              | Input                    |       |

|                        |       |                           |                   | '10'                                                         |                                              | INTERF             | Output                   |       |

|                        |       |                           |                   | '11'                                                         |                                              | N                  | ot Valid                 |       |

|                        |       |                           |                   | SPI/ I <sup>2</sup> C                                        |                                              |                    | T                        | =     |

|                        |       |                           |                   | REG_3[5                                                      | _                                            | Pin Function       | Pin Type                 |       |

| CODE_SEL0              |       |                           |                   | <u> </u>                                                     | fault), '01'                                 | EN_TX              | Input                    |       |

| /EN_TX                 |       | Digital IO                |                   | '10'                                                         |                                              | INTERF             | Output                   | 4     |

| /INTERF                | 13    | 12mA                      |                   | '11'                                                         |                                              | N                  | ot Valid                 |       |

|                        |       |                           |                   | UART                                                         |                                              | T                  | 1                        | 7     |

|                        |       |                           |                   | REG_3[5                                                      |                                              | Pin Function       | Pin Type                 | -     |

|                        |       |                           |                   | '00' (De                                                     | rault)                                       | CODE_SEL1          | Input                    | -     |

|                        |       |                           |                   | '01'                                                         |                                              | BUS_BUSY           | Output                   |       |

|                        |       |                           |                   | '10'                                                         |                                              | N - + \ / -  ; -   |                          | _     |

|                        |       |                           |                   | '11'<br>SPI/ I <sup>2</sup> C                                |                                              | Not Valid          |                          |       |

|                        |       |                           |                   | REG_3[5                                                      | . 41                                         | Pin Function       | Din Type                 | 1     |

|                        |       |                           |                   | '00' (De                                                     | _                                            | BUS_BUSY           | Pin Type<br>Output       | -     |

|                        |       |                           |                   | '01'                                                         | riauit)                                      | BU3_BU31           | Output                   |       |

| CODE SEL1              |       | Digital IO                |                   | '10'                                                         |                                              | -                  |                          |       |

| CODE_SEL1<br>/BUS_BUSY | 12    | 8mA                       |                   | '11'                                                         |                                              | N                  | ot Valid                 | -     |

| 7003_0031              | 12    | Output                    |                   |                                                              | output - His                                 |                    | ission onto the powe     | rline |

| TXON                   | 16    | 12mA                      |                   | is active                                                    |                                              | Bir Wileir Cransin | ission onto the powe     |       |

|                        | 1     |                           |                   |                                                              |                                              | t signal out       |                          |       |

|                        |       |                           |                   | TXON                                                         | REG_1[3]                                     |                    | Impedance [Ω]            |       |

|                        |       |                           |                   | State                                                        |                                              | [V-p-p]            |                          |       |

|                        |       |                           |                   | High                                                         | '0'                                          | 1                  | 18 <sup>1</sup>          |       |

|                        |       |                           |                   |                                                              | '1' (Defau                                   | ılt) 2             |                          |       |

|                        |       |                           |                   | Low                                                          |                                              | High Z             | 5.3k <sup>2</sup>        |       |

|                        |       | Analog Output             |                   |                                                              | utput impe                                   |                    |                          |       |

| TXO                    | 23    | Max 66 mA                 |                   |                                                              |                                              | eferenced to VRI   | EF                       |       |

| RXI                    | 24    | Analog Input              |                   |                                                              | ne receive I                                 | •                  |                          |       |

|                        |       |                           |                   |                                                              |                                              |                    | ering capacitor. Place   |       |

| \ DEE                  | 24    |                           |                   |                                                              |                                              |                    | is used as a virtual gro | ound  |

| VREF                   | 21    | Analog Output             |                   | for the e                                                    | xternai ana                                  | alog circuitry.    |                          |       |

| FILTERI                | 19    | Analog,<br>Bi-directional |                   | Evtornal                                                     | filter I/O                                   |                    |                          |       |

| FILIENI                | 15    | 1                         |                   | External                                                     | iliter 1/O                                   |                    |                          |       |

| FILTERO                | 20    | Analog,<br>Bi-directional |                   | External                                                     | filter I/O                                   |                    |                          |       |

| OSCO                   | 32    | Analog output             |                   |                                                              | Crystal Out                                  | out                |                          |       |

| OSCI                   | 31    | Analog Input              |                   |                                                              | Crystal Inpu                                 |                    |                          |       |

|                        |       |                           |                   | +                                                            |                                              |                    | ance should be max       | imal  |

| L1                     | 27    | Analog Input              |                   | 1pF), see                                                    |                                              | · viz capaciti     |                          |       |

| L2                     | 26    | Analog Input              |                   |                                                              | External inductors L2 (optional), see 2.5.4. |                    |                          |       |

| AVCC                   | 25    | Power                     |                   | Analog 3.3V supply                                           |                                              |                    |                          |       |

| AGND                   | 22,28 | Power                     |                   | Analog g                                                     |                                              |                    |                          |       |

|                        |       |                           |                   | 1.8V core supply output for filtering capacitor. Place 4.7uF |                                              |                    |                          |       |

| VCAP                   | 3     | Power                     |                   | between VCAP and DGND.                                       |                                              |                    |                          |       |

| DGND                   | 4     | Power                     |                   | Digital G                                                    | round                                        |                    |                          |       |

| Name   | Pin # | Pin type | Internal<br>PU/PD | Description                                                 |  |

|--------|-------|----------|-------------------|-------------------------------------------------------------|--|

| DVCC   | 5,14  | Power    |                   | Digital 3.3V supply                                         |  |

| GNDPLL | 30    | Power    |                   | Analog Ground                                               |  |

|        |       |          |                   | PLL 1.8V output to a filtering capacitor. Place 1uF between |  |

| PLLCAP | 29    | Power    |                   | PLLCAP and GNDPLL.                                          |  |

| EXP    | 33    | Power    |                   | Expose pad, should be connected to DGND.                    |  |

PD - Internal Pull-down resistor 50K ohm +/-%30

PU - Internal Pull-up resistor 50K ohm +/-%30

# 2.5 Implementation

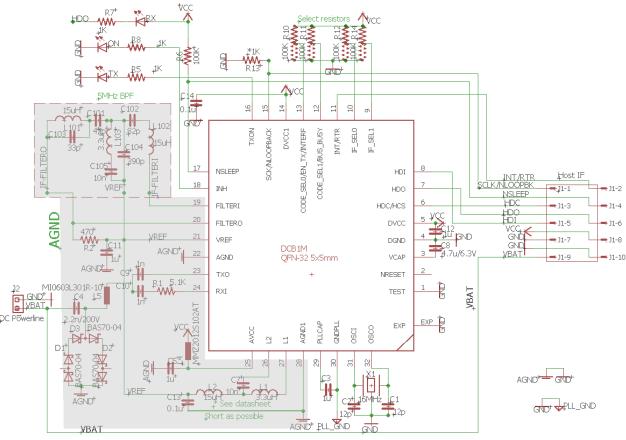

### 2.5.1 DCB1M reference schematic

Figure 4 depicts a typical DCB1M schematic.

Figure 4 - DCB1M reference schematic

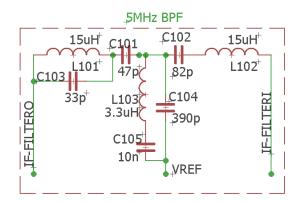

# 2.5.2 External filter (BPF)

The DCB1M operates using an external 5MHz bandpass filter. The minimum allowable bandwidth of the filters is  $\pm$ -700 kHz @ 3dB. Narrower bandwidth limits the maximal bitrate.

Figure 5 depicts a recommended 5MHz discrete passive filter.

Figure 5-5MHz bandpass filter

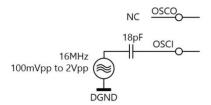

### 2.5.3 External Crystal

The device operates with a low cost, small size 16MHz crystal connected between OSCI and OSCO pins. Each of these pins should be connected to the DGND via a load capacitor. The load capacitors values should be determined according to the crystal manufacturer's recommendations and the actual PCB layout. The PCB traces should be as short as possible.

The overall frequency tolerance should not exceed ± 50ppm.

### 2.5.3.1 Recommended crystals

- o NDK NX2520SA-16MHz, SMD, 2.5x2 mm

- NDK NX3225SA/GB-16MHz, SMD, 3.2x2.5mm

- o NDK NX2016GC-16MHz, SMD, 2.0x1.6mm

- o ECS ECS-160-12-37B-CTN-TR, SMD, 2.0x1.6mm

### 2.5.3.2 16MHz clock from an external source

It is possible to operate the device from an external 16HMz clock source that meets the requirements above. Figure 6 depicts an external 16MHz clock connection to the device.

Figure 6 - External 16MHz clock connection

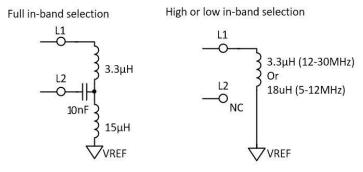

### 2.5.4 L1 and L2 inductors

The DCB1M requires one or two inductors for its operation, depending on the desired operating frequency.

- For full in-band operation, 5MHz 30MHz:

- ➤ L1 3.3uH

- ➤ L2 15uH with 10nF series capacitor between L2 pin and L2 inductor.

- For low in-band operation, 5MHz -12MHz:

- ➤ L1 18uH

- ▶ L2 NC

- For high in-band operation, 12MHz 30MHz:

- ➤ L1 3.3uH

- ▶ L2 NC

Figure 7 depicts the in-band operation inductors' connection to pins L1 and L2.

Figure 7 - L1 and L2 inductors connections

#### 2.5.4.1 Recommended L1 & L2 inductors

Table 2 describes the recommended L1 and L2 inductors.

Table 2 - Recommended L1 and L2 manufacturers

| Inductor | ABRACON              | VISHAY         | TDK               |

|----------|----------------------|----------------|-------------------|

| L1=3.3uH | 815-AIML-0805-3R3K-T | ILSB0805ER3R3K | NL453232T-3R3J-PF |

| L2=15uH  | 815-AIML-0805-150K-T | ILSB0805ER150K | NL453232T-150J-PF |

| L1=18uH  | 815-AIML-0805-180K-T | ILSB0805ER180K | NL453232T-180J-PF |

#### 2.5.5 Optional EMC chip-bead (L5)

For enhanced mitigation of high harmonics above 30MHz conducted over the powerline, it is recommended to add L5 in series to the coupling capacitor C4 (see Figure 4).

Table 3 describes the recommended EMC chip-beads.

Table 3 - Recommended L5 (optional)

| LAIRD | MI0603L301R-10 |  |  |  |  |

|-------|----------------|--|--|--|--|

| LAIRD | HZ0603A222R-10 |  |  |  |  |

| TDK   | MMZ1608Q       |  |  |  |  |

#### 2.5.6 Powerline coupling interface

The DCB1M is coupled to the powerline through a single small footprint coupling capacitor that blocks the DC, typically 2.2nF. The  $C_{\text{coupling}}$  voltage rating depends on the powerline voltage and its expected impulses.

For high voltage powerline applications (e.g. battery monitoring system in EV or solar panels), it is required to add capacitors to achieve full galvanic isolation.

### **External protection network**

It is recommended to add an external diode protection network before the  $C_{\text{coupling}}$ , for protection from high powerline pulses (above 2 V-P-P). The protection network consists of three Schottky diodes serially connected (for both polarities), with low capacitance (< 10pF) and fast clipping (e.g. BAS70-04).

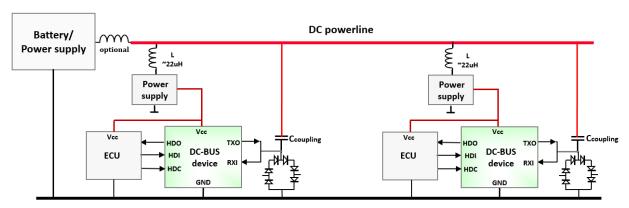

#### 2.5.8 Recommended connection to power-supply

Power-supplies usually require big filtering capacitors that may attenuate strongly the DCB1M carrier signal. It is recommended to add an inductor (>22uH) or ferrite bead (> $100\Omega$  @ 5MHz-30MHz) in series to the power supply connection to the DC powerline to avoid carrier signal attenuation.

Figure 8 depicts a typical DCB1M connection to a DC powerline and its power-supply.

Figure 8 – DCB1M connection to 3.3V power-supply and powerline

#### 3. DCB1M operation

#### 3.1 DCB1M messages

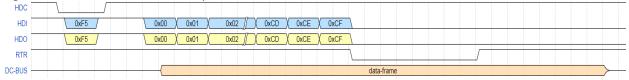

#### 3.1.1 Message structure

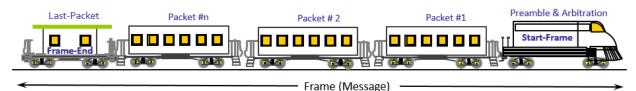

The DCB1M is a message-oriented device. The message is divided by the DCB1M into packets that are encoded against errors and constructed into modulated powerline message (frame).

A frame is constructed from a Start-frame consisting of a preamble and optionally an arbitration sequence (if enabled), followed by packet/s of data bytes (at least 1 packet) and terminated with a "Frame-End" indicating the last packet of the frame.

When Arbitration is enabled, unique arbitration patterns are transmitted before the start-frame preamble pattern (see section 3.6).

Start of frame preamble length

Packet length

- 64usec - 105usec.

- Arbitration pattern length (if enabled)

- **180usec** (codec 0, 1) / **360usec** (codec 2, 3) (see Table 5)

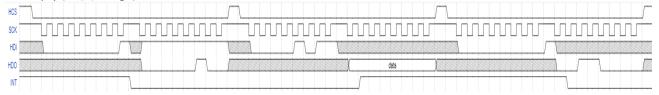

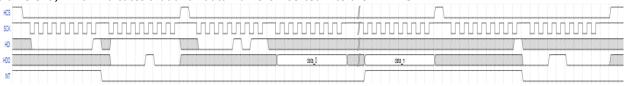

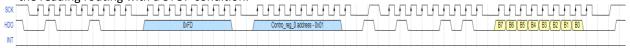

Figure 9 – Frame (Message) structure

An Error Correction Code [ECC] protects each data packet. The user selected powerline bitrate defines also the ECC being used. See section 3.2.2 for more details about codec selection and its configuration.

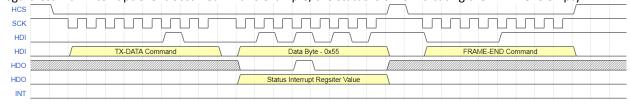

#### 3.1.2 **Transmit flow**

The DCB1M message transmission sequence over powerline depends on the selected interface protocol and

Using the **UART** interface, upon receiving the first data byte from ECU, the Start-frame transmission begins. The message will be closed automatically after all data bytes are extracted from the TX-FIFO (TX-FIFO is empty) and with ECU completion of data bytes transfers.

Using SPI & I'C interfaces, upon receiving the TX-DATA command, a Start-frame transmission begins. The frame is closed upon receiving the FRAME-END indication.

It is recommended to use the INT/RTR pin indication for pausing ECU data byte transfers when needed, to prevent TX-FIFO overflow events. For more details, refer to the protocols handling sections.

The TX-Trigger mode is a special feature that enables the user to control manually when to start the transmission of frame/s. Refer to section 3.4 for more details.

#### 3.1.3 Receive flow

In general, upon detecting a powerline frame, the frame is decoded into data bytes that are inserted into the RX-FIFO.

Using the **UART** interface, each received data byte is inserted into the RX-FIFO and then, automatically transferred to the ECU. The data transfer to the ECU will continue as long as the RX-FIFO is not empty.

11 DS-DCB1M R 0.83 www.yamar.com Tel: +972-3-5445294 Fax: +972-3-5445279

Using **SPI & I<sup>2</sup>C** interfaces, ECU shall use the interrupt to perform an *RX-DATA* command to extract the stored RX-FIFO data bytes. For more details, refer to the protocols handling sections.

### 3.2 Device configuration

### 3.2.1 Protocol interfaces

The DCB1M interfaces with UART, SPI, and I<sup>2</sup>C protocols. The selected interface protocol is set after reset/power-up and stays valid until the next reset/power-cycle event.

DCB1M pins 9 and 10 (IF\_SEL[1:0]) configure the interface selection as described in Table 1 and Table 4.

**Table 4 - Protocols Selection**

| Tubic 1 110totolo ocicotion |                   |  |  |  |  |

|-----------------------------|-------------------|--|--|--|--|

| IF_SEL[1:0]                 | Selected Protocol |  |  |  |  |

| 00                          | UART              |  |  |  |  |

| 01                          | Reserved          |  |  |  |  |

| 10                          | SPI               |  |  |  |  |

| 11                          | I2C               |  |  |  |  |

### 3.2.2 Codec selection

The DCB1M has four levels of error correction coding (ECC). Code 3 has the strongest data protection against powerline noises with the lowest powerline bitrate. ECU may select different codes for each frame.

The DCB1M codec selection can be set in various methods, depending on the selected interface.

In the UART interface, the user can set the codec selection either by using pins 12 and 13 (see section 2.3) or by configuring REG\_0[1:0] bits. Both methods have the same priority and the last configuration change will determine the DCB1M codec selection. For example, after power-up/reset, the DCB1M will read the status of pins 12 and 13, and set the codec selection accordingly. Then, the user may change the codec selection by configuring REG\_0[1:0] differently. The codec selection will change accordingly.

Table 5 describes the DCB1M codecs and their max bitrates over powerline.

**Table 5 - Codec Selection**

| <b>Codec Select</b> | Max powerline bitrate (Mbit/s) | CODE_SEL1,CODE_SEL0 | REG_0[1:0] |

|---------------------|--------------------------------|---------------------|------------|

| Code 0              | 1.4                            | Low, Low            | '00'       |

| Code 1              | 1                              | Low, High           | '01'       |

| Code 2              | 0.5                            | High, Low           | '10'       |

| Code 3              | 0.225                          | High, High          | '11'       |

In SPI and I<sup>2</sup>C protocol interfaces, the user sets the codec selection inherently in the *TX-DATA* Command. Please refer to section 7.5.1 or 8.5.1 for more information.

# 3.2.3 DCB1M TX-FIFO and RX-FIFO handling

The DCB1M consists of 1024 bytes TX-FIFO and 1024 bytes RX-FIFO to buffer data between the ECU and the DCB1M. The TX-FIFO stores all the data bytes from the ECU HDI pin. Each frame stored in the TX-FIFO, contain also two extra control bytes that are not transmitted over the powerline. This information is relevant when multiple frames are stored and TX-Trigger mode enabled (see 3.4).

The RX-FIFO stores all the data bytes received from the powerline, before its transfer to the ECU via HDO pin. Each frame constructed in the RX-FIFO contains an extra control byte that is not transferred to the ECU.

See below section's examples of FIFOs threshold handling.

### 3.2.3.1 FIFOs interrupt thresholds configuration

Users may define FIFOs interrupts status thresholds according to the network expected payload. The interrupt is invoked on INT/RTR pin 11 (for **UART** see 6.5, for **SPI** see 7.4, for  $I^2C$  see 8.3).

The FIFOs interrupt threshold control registers are described in Table 6.

Table 6 - FIFOs Interrupts threshold control

| FIFO Threshold    | Default threshold | Related Control | Comments                                                          |

|-------------------|-------------------|-----------------|-------------------------------------------------------------------|

| Description       | [Data bytes]      | registers       |                                                                   |

| Rx-FIFO-not-empty | 256               |                 | Applicable to SPI & I2C Only. Defines how many                    |

| [9:0]             |                   | REG_6[1:0],     | data bytes are inserted to RX-FIFO before the                     |

|                   |                   | REG_5[7:0]      | interrupt raise. Indicate the ECU to start reading                |

|                   |                   |                 | the received frame. See                                           |

|                   |                   |                 |                                                                   |

|                   |                   |                 | Example 1 - Rx-FIFO-not-empty threshold <b>setting</b>            |

| Tx-FIFO-almost-   | 1012              | REG_3D[1:0],    | For SPI & I <sup>2</sup> C:                                       |

| full[9:0]         |                   | REG_3C[7:0]     | Defines how many bytes inserted to the TX-FIFO                    |

|                   |                   |                 | before the interrupt rises, Indicates the ECU to                  |

|                   |                   |                 | stop transferring data to the DCB1M before TX-                    |

|                   |                   |                 | FIFO overflow may occur.                                          |

|                   |                   |                 | For UART:                                                         |

|                   |                   |                 | The RTR will always drop when TX-FIFO is inserted                 |

|                   |                   |                 | with >= 1022 bytes. The RTR remains low until TX-                 |

|                   |                   |                 | FIFO is below the TX-FIFO-almost-full[9:0]                        |

|                   |                   |                 | threshold. During RTR low time, ECU must stop                     |

|                   |                   |                 | transferring data to the DCB1M.                                   |

|                   |                   |                 | See Example 2 - Tx-FIFO-almost-full threshold                     |

|                   |                   |                 | setting                                                           |

| Tx-FIFO-almost-   | 12                | REG_3E[5:0],    | Applicable to SPI & I <sup>2</sup> C Only. Allow user to re-start |

| empty [9:0]       |                   | REG_3D[7:4]     | data transfer to the TX-FIFO safely, until Tx-FIFO-               |

|                   |                   |                 | almost-full event. Example 3 - Tx-FIFO-almost-                    |

|                   |                   |                 | empty threshold setting                                           |

### Example 1 - Rx-FIFO-not-empty threshold setting

Configuration Rx-FIFO-not-empty threshold to 0x384 results in interrupt triggering when there are at least 900 data bytes are stored in Rx-FIFO:

REG 6 = 0x03

$REG_5 = 0x84$

### Example 2 - Tx-FIFO-almost-full threshold setting

The Tx-FIFO-almost-full interrupts indicate when the ECU transmitter needs to pause any data transfer to prevent the Tx-FIFO overflow event.

In general, in the case of an interrupt event on Tx-FIFO-almost-full, data transfer should be paused until the interrupt on *Tx-FIFO-almost-empty* is received.

It is recommended to configure the TX-FIFO<sub>almost full thrs</sub> as given in Definition of equation (1).

Definition of equation

$$TX\text{-}FIFO_{almost\_full\_thrs} = \left(\frac{1024}{bytes\ per\ frame + 2}\right)*\ bytes\ per\ frame \tag{1}$$

**EXAMPLE A**

ECU sends 30 data bytes in each frame:

$$TX\text{-}FIFO_{almost\_full\_thrs} = \left(\frac{1024}{30+2}\right) * 30 = 960$$

**EXAMPLE B**

ECU sends 500 data bytes per frame:

$$TX\text{-}FIFO_{almost\_full\_thrs} = \left(\frac{1024}{500+2}\right) * 500 = 1019.9 = 1019$$

### Example 3 - Tx-FIFO-almost-empty threshold setting

The *Tx-FIFO-almost-empty* interrupts indicate when the ECU transmitter can re-start its byte transfer after the transmission paused due to *Tx-FIFO-almost-full* previous event.

It is recommended to configure the TX-FIFO<sub>almost empty thrs</sub> as given in Definition of equation(2).

### **Definition of equation**

$$TX-FIFO_{almost\ empty\ thrs} = TX-FIFO_{almost\ full\ thrs} - Bytes\ per\ frame$$

(2)

### With EXAMPLE A:

TX- $FIFO_{almost\_empty\_thrs} = 960 - 30 = 930$

### With EXAMPLE B:

TX-FIFO<sub>almost empty thrs</sub> = 1019 - 500 = 519

For more details, please refer to the RTR/INT handling in each one of the protocol's sections.

### 3.2.3.2 FIFOs reset control (Soft-Reset event)

ECU may reset the TX-FIFO and RX-FIFO stored data by activating a DCB1M Soft-reset event.

Using the **UART** interface, a *Soft-reset* is activated while the HDC pin 6 is low.

Using SPI & I'C interfaces, a Soft-reset is activated while performing a WRITE-REG command to REG 2<sup>1</sup>.

During *Soft-reset*, the DCB1M performs only write and read to/from DCB1M control registers. Neither transmission nor reception to/from the powerline is available. The TX-FIFO and RX-FIFO are kept in reset.

### 3.3 Carrier frequency configuration

Users can define carrier frequency from 5MHz to 30MHz with a spacing of 100 kHz (Total of 251 selectable carriers). The active carrier frequency selection is made by configuring REG\_2 (see 5.3). Upon completion of configuration, the DCB1M will update its operating carrier frequency within 1msec. During this 1msec period, the DCB1M is kept in Soft-reset and will not communicate with its ECU nor detect new frames (messages) from the powerline.

When setting multiple DCB1M networks to operate over a single powerline, it is recommended to select carrier frequencies spaced more than 1.5MHz from each other.

The carrier-selected value is calculated as given in the Definition of equation (3).

### **Definition of equation**

$$REG_2 = (Carrier Freq. [MHz] - 5) * 10$$

(3)

# **EXAMPLE 1**

❖ When setting the frequency to 14.1MHz:

$$REG_2 = (14.1 - 5) * 10 = 0x5B$$

### **EXAMPLE 2**

❖ When Setting to 5MHz:

$$REG_2 = (5 - 5) * 10 = 0x00$$

### 3.3.1 Pins 12-13 IO function control

The DCB1M pins 13 and 12 have several configurable functionalities, as describes in Table 7 and Table 8.

- ➤ **CODE\_SELO and CODE\_SEL1** digital inputs, for codec selecting in UART only.

- **EN\_TX** digital input enables manual transmission over the powerline (see section 3.4).

- ➤ INTERF digital output high while an interference signal is being detected in the operating carrier frequency.

- **BUS\_BUSY** digital output, high when DCB1M is transmitting over the powerline or during the reception from the powerline. This function can be used to monitor the status of the powerline channel and act accordingly (wait for the completion of reception and transmission).

Table 7 - UART Interface pins functionality

| REG_3[5:4]     | Pin 13 Function | Pin 13 Type | Pin 12 Function | Pin 12 Type |

|----------------|-----------------|-------------|-----------------|-------------|

| '00' (Default) | CODE_SEL0       | Input       | CODE_SEL1       | Input       |

| '01'           | EN_TX           | Input       | BUS_BUSY        | Output      |

| '10'           | INTERF          | Output      |                 |             |

<sup>&</sup>lt;sup>1</sup> It is recommended to always configure REG\_2 last during the DCB1M configuration routine by the user (if the configuration is required).

Table 8 - SPI & I<sup>2</sup>C Interface pins functionality

| REG_3[5:4]           | Pin 13 Function | Pin 13 Type | Pin 12 Function Pin 12 Type |        |  |

|----------------------|-----------------|-------------|-----------------------------|--------|--|

| '00' (Default), '01' | EN_TX           | Input       | BUS_BUSY                    | Output |  |

| '10'                 | INTERF          | Output      |                             |        |  |

| '11'                 | Not Valid       |             | Not Va                      | alid   |  |

### 3.3.2 TXO output level and drive control

The TXO pin output level and drive capability to the powerline are controlled by REG\_1[3], as described in Table 9.

Table 9 - TXO signal level

| TXON State | REG_1[3]      | TX level [V-p-p] |

|------------|---------------|------------------|

| High       | '0'           | 1                |

|            | '1' (Default) | 2                |

| Low (Rx)   |               | High Z           |

Setting the TXO output drive capability is made by configuring REG\_1[0], as described in Table 10.

Table 10- TXO output drive control

| TXON State | REG_1[0]      | Output drive [A] | Impedance [Ω]     |

|------------|---------------|------------------|-------------------|

| High       | '0' (Default) | 33mA             | 18 <sup>1</sup>   |

|            | '1'           | 66mA             |                   |

| Low (Rx)   |               | Disabled         | 5.3k <sup>2</sup> |

<sup>&</sup>lt;sup>1</sup>Series output impedance

### 3.4 TX-Trigger mode

As explained in section 3.1.2, in TX Normal mode, as soon as the TX-FIFO is filled with data byte, a powerline frame transmission begins. The *TX-Trigger* mode disables the auto frame transmission. ECU can manually <u>start</u> a frame transmission over the powerline.

The *TX-Trigger* mode is enabled by setting <u>REG\_0[5]</u>, along with setting pin 13 to EN\_TX and pin 12 to BUS\_BUSY functionality (see section 3.3.1).

### 3.4.1 TX-Trigger mode - UART interface handling

When TX trigger mode is enabled, each data byte is transferred from ECU to the TX-FIFO. The DCB1M will not start automatically a frame transmission over the powerline. To start the frame transmission, ECU shall toggle the EN\_TX pin high for at least 100nsec and then pull it low. The new frame transmission starts and will automatically end when TX-FIFO is empty and ECU finishes data bytes transfers.

# 3.4.2 TX-Trigger mode - SPI & I<sup>2</sup>C interface handling

When TX trigger mode is enabled, each data byte transferred from ECU is stored in the TX-FIFO. The DCB1M will not start automatically a frame transmission over the powerline. To start a powerline frame transmission, ECU shall toggle the EN\_TX pin high for at least 100nsec and then pull it low.

The new frame transmission starts and will automatically end at the first *FRAME-END* command extracted from TX\_FIFO. It means that the user may insert multiple frames into the TX-FIFO by sending the TX-DATA command, followed by frame data bytes, followed by the *FRAME-END* command, multiple times. Each one of the frames is transmitted separately according to the EN\_TX toggle event.

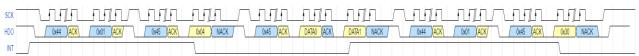

For example, SPI ECU transfers the following sequence of 2 frames as described in Table 11.

Table 11 - SPI multiple frames example

|                   | rable 11 - 3r i multiple frames example |       |                                |  |  |  |  |  |

|-------------------|-----------------------------------------|-------|--------------------------------|--|--|--|--|--|

|                   | ECU bytes transfer                      | Frame | Comment                        |  |  |  |  |  |

| 1.                | TX-DATA command                         | Α     | start-of-frame byte of Frame A |  |  |  |  |  |

| 2.                | Data byte 0x44                          |       | Frame A first data byte        |  |  |  |  |  |

| 3. Data byte 0x10 |                                         |       | Frame A second data byte       |  |  |  |  |  |

| 4.                | FRAME-END command                       |       | end-of-frame byte of Frame A   |  |  |  |  |  |

| 5.                | TX-DATA command                         | В     | start-of-frame byte of Frame B |  |  |  |  |  |

| 6.                | Data byte 0x33                          |       | Frame B only data byte         |  |  |  |  |  |

Tel: +972-3-5445294 Fax: +972-3-5445279

www.yamar.com

<sup>&</sup>lt;sup>2</sup>Input impedance referenced to VREF

| 7. FRAME-END command | end-of-frame byte of Frame B |

|----------------------|------------------------------|

|----------------------|------------------------------|

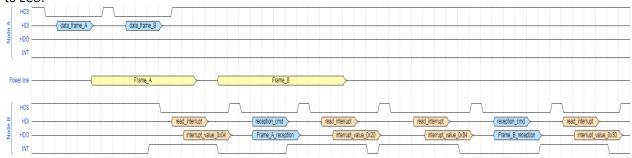

At this point, the TX-FIFO holds two separated frames, frame A contains two data bytes (0x44 and 0x10), and frame B contains one data byte (0x33).

At the first EX\_TX toggle, frame A is transmitted. With the second EN\_TX toggle, frame B is transmitted.

In general, the user may use the BUS\_BUSY pin for an indication of whether the DC-BUS is idle to start new frame transmission.

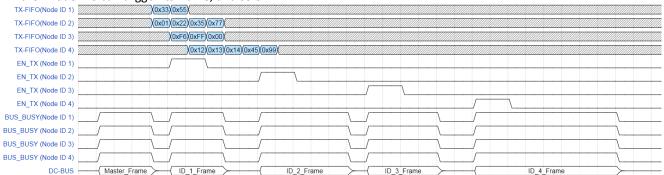

Figure 10 depicts a TX-Trigger network example. In this example, one DCB1M network contains five nodes (Assigned with ID 0 to 4). A master node (ID0) transmits a broadcast information request to all four nodes. All other DCB1M nodes will decode the message whereas only node ID1 shall respond first. During the node ID0 response frame, the rest of the nodes can gather their information and transfer it to their DCB1M TX-FIFO. After node IDO completed its response frame, the BUS\_BUSY pin will go low, then node ID2 can trigger its stored frame, then node ID3 can trigger its frame, and so on.

Figure 10 - TX-Trigger example

#### 3.5 Carrier Sense mode (CS)

The Carrier Sense (CS) allows the DCB1M to sense the powerline before starting transmission. It prevents interfering with other DCB1M node's transmission. In this mode, the DCB1M check if the DC-BUS (powerline channel) is idle or if there is currently an ongoing frame transmission. When CS is enabled and the ECU starts to transfer data bytes to the DCB1M, the device will start transmission only if the DC-BUS is idle. If the DC-BUS is not idle, the device will wait until the DC-BUS idle again, and only then, the transmission will start. To enable the CS mode, set <a href="REG\_0[3">REG\_0[3]</a> to high (Default CS is disabled).

#### 3.6 Arbitration mode (ARB)

The Arbitration mode is used to prioritize messages over powerline in multiple Master network topology. If two or more devices try to gain access to the DC-BUS at the same time, the arbitration mechanism is used to allow the message with higher priority (lower arbitration ID) to gain access and transmit its message over the DC-BUS. When Arbitration mode is enabled, the message will begin with a carrier sense period followed by the arbitration sequence. If the arbitration has passed successfully then the DCB1M will proceed with data frame transmission, else, the DCB1M will abort the transmission and will wait for the received message from other DCB1M to finish before automatically try to retransmit. The total arbitration period is 105usec. The arbitration ID is user-defined by configuring the Arbitration ID[10:0] stored in REG 7 and REG 8.

To enable the Arbitration mode, set REG 0[4] high (Default ARB is disabled).

#### 3.7 DCB1M UUID

Each DCB1M device is hard-coded with a 48 bit universally unique identifier (UUID[47:0]).

The UUID is stored in REG\_59 to REG\_5E and can be retrieved using the READ-REG commands (see 5.14 to 5.19).

#### 4. Power operation modes

The DCB1M has three power operation modes; Normal, Standby, and Sleep.

© 2015 - 2021 Yamar Electronics Ltd. www.yamar.com

### 4.1 Normal mode

In Normal mode, the DCB1M is either in RX mode, listening for a powerline message, or in TX mode, transmitting a message over the powerline.

### 4.2 Standby mode

The DCB1M enters Standby mode upon wake-up from Sleep mode, while the NSLEEP pin is still low. The DCB1M is kept in *Soft-reset*, whereas communication with the ECU is suspended until the NSLEEP pin is set High.

# 4.3 Sleep modes (power-saving)

The DCB1M has four Sleep modes for best power consumption/performance during Sleep. During this mode, only a small amount of hardware is operational mainly to detect wake-up messages (*WUM*) from the powerline and returning to Normal mode operation.

Table 12 describes the DCB1M sleep modes.

Table 12 - Sleep modes description

| Sleep mode               | Description                                                                                                    | Typical Power   | Performance                                                              |

|--------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------|

|                          |                                                                                                                | consumption [A] |                                                                          |

| Enhanced sleep<br>(SLP1) | The device wakes-up every 32ms to sense the powerline for WUM detection.                                       | 120μ            | Wake-up detection with-in 64mSec. Best detection in a noisy environment. |

| Fast wake-up<br>(SLP2)   | The device continuously monitors the powerline for WUM detection.                                              | 1000μ           | Fast wake-up detection with-in 250uSec.                                  |

| Low-power<br>(SLP3)      | The device wakes-up every 32ms to sense the powerline for WUM detection.                                       | 85μ             | Wake-up Detection with-in 64mSec.                                        |

| Deep Sleep<br>(SLP4)     | The device does NOT wake-up to sense for bus activity, staying in deep sleep. Wake-up only locally by the ECU. | 65μ             | No bus wake-up detection.                                                |

The Sleep modes use four interface pins as described in Table 13.

**Table 13- Sleep interface pins**

| NSLEEP | Digital | High - Normal mode is active.                                                         |  |  |  |  |  |  |

|--------|---------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        | input   | Low - Sleep /Standby mode is active.                                                  |  |  |  |  |  |  |

| INH    | Digital | Output indication to Inhibit ECU.                                                     |  |  |  |  |  |  |

|        | output  | High - Normal mode is active.                                                         |  |  |  |  |  |  |

|        |         | Low - Sleep mode is active.                                                           |  |  |  |  |  |  |

| HDO    | Digital | Normal mode - data output to ECU.                                                     |  |  |  |  |  |  |

|        | output  | Sleep/Standby mode - asserted low while the wake-up message is being                  |  |  |  |  |  |  |

|        |         | detected/transmitted over the powerline.                                              |  |  |  |  |  |  |

| HDC    | Digital | Normal mode - ECU Command mode / chip select.                                         |  |  |  |  |  |  |

|        | input   | Sleep mode - ECU wakes-up the DCB1M locally by toggling the HDC high-low-high. The    |  |  |  |  |  |  |

|        |         | DCB1M then exit the Sleep mode to Standby mode (NSLEEP still asserted low), or Normal |  |  |  |  |  |  |

|        |         | mode (NSLEEP is high).                                                                |  |  |  |  |  |  |

# 4.3.1 Wake-up message (WUM)

When Auto-WUM is enabled (REG[3]='1'), upon the rise of the NSLEEP pin, the DCB1M transmits a broadcast WUM over the powerline, to wake-up all network-connected devices.

ECU can configure the length of the WUM as described in Table 14.

Table 14 - Wake-up message length configuration

| REG_3[2] | Wake-up message length                |  |  |  |  |

|----------|---------------------------------------|--|--|--|--|

| 0        | SLP2 - 250usec / SLP1, SLP3 - 75msec  |  |  |  |  |

| 1        | SLP2 - 1.5msec / SLP1, SLP3 - 150msec |  |  |  |  |

During WUM transmission, the HDO pin is asserted low until WUM transmission is completed, indicating to the ECU the wake-up process status. ECU shall wait for the HDO rise, before initiating new bytes transfer.

www.yamar.com Tel: +972-3-5445294 Fax: +972-3-5445279

#### 4.3.2 **Entering Sleep mode**

During Sleep mode, the device is kept in a Soft-reset state and will not transfer data bytes from the ECU nor receive data frames from the powerline. When the device enters Sleep mode, the INH pin is asserted low. There are two ways to enter Sleep mode;

#### 4.3.2.1 **Enter Sleep by NSLEEP**

By asserting the NSLEEP pin low, the DCB1M will enter Sleep mode.

#### **Enter Sleep by register setting** 4.3.2.2

By setting REG 3[7] high, the DCB1M will enter Sleep mode, and reset automatically REG 3[7] to low.

### **Exiting Sleep mode**

There are three ways to exit Sleep mode. When exiting Sleep mode, the INH pin is raised and the device switches to Standby or Normal mode.

### Exit Sleep by WUM detection

Upon detection of a WUM, the device immediately exits Sleep mode, INH pin rises and the device enters Standby

In case the NSLEEP pin is low, the device remains in Standby mode, where the device is kept in Soft-reset.

In case the NSLEEP pin is high, the device immediately switches to Normal mode.

During WUM reception, the HDO pin is asserted low until WUM reception is completed, indicating the ECU on the wake-up process status. ECU shall wait for HDO to rise, before initiating new bytes transfer.

#### 4.3.3.2 Exit sleep by NSLEEP pin

Upon detection of NSLEEP pin rise, the device immediately exits Sleep mode, INH pin rises, and enters Normal mode. When Auto-WUM is enabled, a WUM is transmitted over the powerline (see 4.3.1).

#### 4.3.3.3 **Exit Sleep by toggling HDC**

Upon detection of HDC pin toggle high-low-high, the device immediately exits Sleep mode, INH pin rises, and enters Standby mode.

In case the NSLEEP pin is still low, the device remains in Standby mode, where the device is kept in Soft-reset.

In case the NSLEEP pin is high, the device immediately switches to Normal mode.

In this case, the WUM will NOT be transmitted over the powerline.

ECU shall use the HDC pin to exit Sleep mode when the NSLEEP pin is not connected.

### Sleep modes description

ECU can select between four Sleep modes (see 5.4).

#### 4.3.4.1 Enhanced Sleep mode (SLP1)

By setting REG\_3[1:0] = '00', the enhanced Sleep mode (SLP1) is selected.

When entering SLP1, the device wakes-up every 32ms periodically to monitor (sense period) for activity on the powerline. If a WUM is detected, the device exit Sleep modes as described in section 4.3.3.1, otherwise the device return to Sleep mode until the next sense period, and so on...

# Fast wake-up Sleep mode (SLP2)

By setting REG 3[1:0] = '01', the Fast wake-up Sleep mode (SLP2) is selected. The device continuously monitors the powerline for WUM detection. It allows fast WUM detection within 250usec. When WUM is detected, the device exit Sleep mode as described in section 4.3.3.1.

#### 4.3.4.3 Low-power Sleep mode (SLP3)

By setting REG\_3[1:0] = '10', the low-power mode (SLP3) is selected. The device wakes-up every 32msec periodically to monitor (sense period) for activity on the powerline. If a WUM is detected, the device exit Sleep modes as described in section 4.3.3.1, otherwise the device return to Sleep mode until the next sense period.

18 DS-DCB1M R 0.83 Tel: +972-3-5445294 Fax: +972-3-5445279 www.yamar.com

### 4.3.4.4 Deep Sleep mode (SLP4)

By setting REG\_3[1:0] = '11', the Deep Sleep mode (SLP4) is selected. The device will NOT wake-up to monitor (sense) the powerline for activity, rather than stay in deep sleep, whereas all its analog resources are shut down to maintain the lowest power consumption.

The device can exit Deep Sleep mode locally only, either by the NSLEEP or by HDC pins (see 4.3.3.2 and 4.3.3.3).

### 4.3.5 Sleep modes Examples

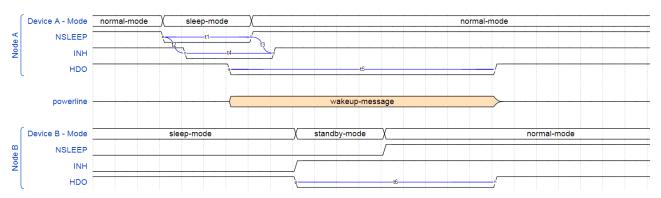

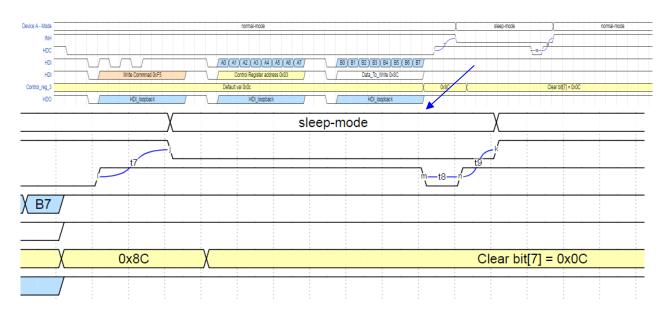

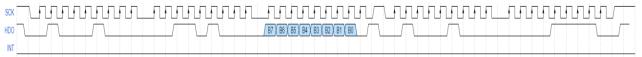

# 4.3.5.1 Sleep Example 1 - Enter by NSLEEP, Exit Sleep mode by NSLEEP & WUM

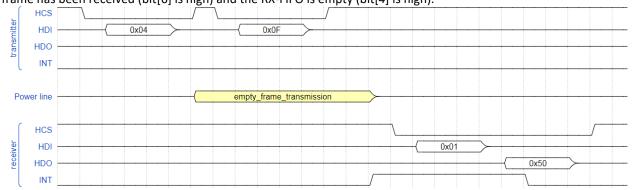

Figure 11 depicts entering sleep by NSLEEP and exit sleep by NSLEEP pin (Node A) and WUM detection (Node B). In this example, the ECU wakes-up device Node A by raising the NSLEEP pin. Upon pull-up the NSLEEP pin, the INH pin is raised and a WUM is transmitted over the powerline (*Auto-WUM* is enabled) to wake-up Node B. While transmitting the WUM, device Node A asserts HDO pin low. After completion of WUM transmission, the HDO is raised again (can be used as signal/interrupt to ECU). At the Node B side, during its sensing period (e.g. *SLP1*), the WUM is detected, and the INH rises while switching to Standby mode. Node B HDO pin is asserted low for the reaming duration of WUM reception. Then, ECU Node B raises the NSLEEP pin and the device switches to Normal mode.

Figure 11 - Enter sleep by NSLEEP, Exit sleep by NSLEEP & WUM

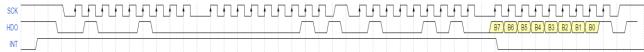

# 4.3.5.1 Sleep Example 2 - Enter sleep by control register bit, exit sleep by HDC

Figure 12 depicts entering sleep by setting REG\_3[7] high and exiting Sleep mode by toggling the HDC pin. In this example, ECU configured REG\_3[7] high using Command mode (UART interface), the device enters Sleep mode, and INH pin drops. After a while, ECU toggle HDC pin low to high, and the device exits Sleep mode without transmitting the WUM, raising the INH pin and switching to Normal mode again.

Figure 12 - Enter sleep by control register bit, Exit sleep by HDC

20

DS-DCB1M R 0.83

# 5. DCB1M Registers

The DCB1M contains internal registers for configuration and status checks. Each of these registers is accessible by the ECU for *Read* and *Write* operations. The access to these registers is different for each interface protocol and described in the protocol interfaces sections. This section elaborates on the registers and their default values after power-up/reset. Also, a read-only byte containing the Interrupt status can be fetched with SPI and I<sup>2</sup>C interfaces.

Table 15 - Registers summary table

| Register name                             | Addr. | Description                                               |  |

|-------------------------------------------|-------|-----------------------------------------------------------|--|

| REG_0 - 'Device Control 0'                | 0x00  | Codec selection, Loopback, Arbitration, Carrier sense     |  |

| REG_1 - 'Device Control 1'                | 0x01  | Transmit level control                                    |  |

| REG_2 - 'Frequency Select'                | 0x02  | Carrier frequency selection                               |  |

| Reg_3 - 'Sleep & IO Control'              | 0x03  | Sleep modes and IO pins                                   |  |

| REG_4 - 'Interrupts Enable'               | 0x04  | Enable Interrupts control                                 |  |

| REG_5 - 'Interrupt RX-FIFO Threshold 1'   | 0x05  | RX-FIFO not empty threshold lower nibble                  |  |

| REG_6 - 'Interrupt RX-FIFO Threshold 2',  | 0x06  | RX-FIFO not empty threshold higher nobble, device errors  |  |

| Device error status                       |       | status                                                    |  |

| REG_3C - 'Interrupt TX-FIFO Thresholds 1' | 0x3C  | Tx-FIFO almost full threshold lower nibble                |  |

| REG_3D - 'Interrupt TX-FIFO Thresholds 2' | 0x3D  | Tx-FIFO almost full threshold higher nibble, Tx-FIFO almo |  |

|                                           |       | empty threshold lower nibble                              |  |

| REG_3E - 'Interrupt TX-FIFO Thresholds 3' | 0x3E  | FIFO almost empty threshold high nibble                   |  |

| REG_7 - 'Arbitration ID 1'                | 0x07  | Arbitration Id low nibble                                 |  |

| REG_8 - 'Arbitration ID 2'                | 0x08  | Arbitration Id higher nibble                              |  |

| Status Interrupt byte                     |       | Interrupts status (Accessible by READ-INT command during  |  |

|                                           |       | TX-DATA routine, SPI, I <sup>2</sup> C only).             |  |

| REG_59 - DCB1M UUID[47:40]                | 0x59  | Read only - UUID[47:40]                                   |  |

| REG_5A - DCB1M UUID[39:32]                | 0x5A  | Read only - UUID[39:32]                                   |  |

| REG_5B - DCB1M UUID[31:24]                | 0x5B  | Read only - UUID[31:24]                                   |  |

| REG_5C - DCB1M UUID[23:16]                | 0x5C  | Read only - UUID[23:16]                                   |  |

| REG_5D - DCB1M UUID[15:8]                 | 0x5D  | Read only - UUID[15:8]                                    |  |

| REG_5E - DCB1M UUID[7:0]                  | 0x5E  | Read only - UUID[7:0]                                     |  |

# 5.1 REG\_0 - 'Device Control 0' (Address 0x00)

|   | Bit 7    | Bit 6     | Bit 5        | Bit 4       | Bit 3          | Bit 2   | Bit 1        | Bit 0        |

|---|----------|-----------|--------------|-------------|----------------|---------|--------------|--------------|

| ſ | R        | R/W [1]   | R/W [0]      | R/W [0]     | R/W [0]        | R/W [0] | R/W [1]      | R/W [1]      |

| Ī |          |           | Enable Tx    | Enable      | Enable carrier |         |              |              |

|   | Reserved | nLoopBack | trigger mode | arbitration | sense          | 0       | Codec_Sel[1] | Codec_Sel[0] |

Bit [1:0] - Codec Select - Selects the coding strength (Maximal powerline bitrate) of the transmitted message (UART only, see 3.2.2).

Bit [2] - '0'

Bit [3] - Enable Carrier Sense mode (see section 3.5).

Bit [4] - Enable Arbitration mode (see section 3.6).

Bit [5] - Enable TX trigger mode (see section 3.4).

Bit [6] - 'nLoopBack' -Set this bit to disables loopback between HDI to HDO (UART only)

Bit [7] - Reserved

R - Readable bit, W - Writeable bit [x] - Value on power-up. '1' - bit is set; '0' - bit is cleared

# 5.2 REG\_1 - 'Device Control 1' (Address 0x01)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3           | Bit 2 | Bit 1 | Bit 0      |

|-------|-------|-------|-------|-----------------|-------|-------|------------|

| [1]   | [1]   | [1]   | [1]   | R/W [1]         | [0]   | [0]   | R/W [0]    |

|       |       |       |       |                 |       |       | Enable TXO |

| 1     | 1     | 1     | 1     | TX signal level | 0     | 0     | high power |

Bit [0] - Enable TXO high power. Set this bit to enable maximal TXO drive of 66mA, clear this bit for maximal TXO drive of 33mA (see section Table 10).

Bit [1] - '0' Bit [2] - '0'

Bit [3] - TX signal level control at TXO pin: '0' = 1Vpp, '1'- 2Vpp (see section 3.3.2).

Bit [7:4] - '1111'

<u>ar.com</u> Tel: +972-3-5445294 Fax: +972-3-5445279

R - Readable bit,

W - Writeable bit [x] - Value on power-up. '1' - bit is set; '0' - bit is cleared

#### 5.3 REG 2 - 'Frequency Select' (Address 0x02)

| Bit 7                           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |

|---------------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| R/W [0]                         | R/W [1] | R/W [0] | R/W [1] | R/W [0] | R/W [0] | R/W [0] | R/W [0] |  |

| Carrier Frequency Configuration |         |         |         |         |         |         |         |  |

Bits [7:0] - Carrier Frequency configuration from in-band. Default configuration is 13MHz

(See section 3.3 - Carrier frequency configuration).

#### 5.4 REG\_3 - 'Sleep & IO Control' (Address 0x03)

|   | Bit 7      | Bit 6 | Bit 5                        | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   |

|---|------------|-------|------------------------------|---------|----------|----------|---------|---------|

|   | W [0]      | [0]   | R/W [0]                      | R/W [0] | R/W [1]  | R/W [1]  | R/W [0] | R/W [0] |

| Ε | nter Sleep | 0     | pin 12 and pin 13 functional |         | Auto WUM | Long WUM | Sleep   | modes   |

|   | mode       |       | selection                    |         |          |          | seled   | ction   |

Bit [1:0] - '00' - Enhanced Sleep mode [SLP1], '01' -Fast wake-up Sleep mode[SLP2], '10' - Low-power sleep mode [SLP3], '11' - Deep Sleep mode [SLP4] (see section4.3).

Bit [2] - Control powerline wake-up message duration (see Table 14).

Bit [3] -Auto wake-up message (WUM): '0' disables transmission of WUM after wakeup from NSLEEP pin.

Bits [5:4] - Device pin 12 and pin 13 functional selection (see section 3.3.1).

Bit [6]

Bit [7] - Enter Sleep mode reg. Instead of entering Sleep mode through the NSLEEP pin, the user can activate the Sleep mode selected in bits [1:0], by setting bit[7]. After entering Sleep mode, bit [7] is automatically cleared to '0'.

R - Readable bit,

W - Writeable bit

[x] - Value on power-up. '1' - bit is set; '0' - bit is cleared

#### 5.5 REG 4 - 'Interrupts Enable (Address 0x04) (SPI & I<sup>2</sup>C Only)

| Bit 7                                          | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |  |

|------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| W/R[1]                                         | R/W [0] | R/W [1] |  |

| SPI & I <sup>2</sup> C Interrupts Enable [7:0] |         |         |         |         |         |         |         |  |

<sup>&#</sup>x27;1' -Interrupt bit is enabled.

Bit [0] - Tx-FIFO-almost-full enable bit

Bit [1] - Tx-FIFO-almost-empty enable bit

Bit [2] - Rx-frame-end enable bit – Must share the same state as Bit [5] (enabled or disabled).

Bit [3] - Rx-FIFO-not-empty enable bit

Bit [4] - Rx-FIFO-empty enable bit

Bit [5] - End-of-frame (EOF) enable bit – Must share the same state as Bit [2] (enabled or disabled).

Bit [6] - Empty-frame enable bit (Default disabled)

Bit [7] - Error-flag enable bit

R - Readable bit,

W - Writeable bit [x] - Value on power-up. '1' - bit is set; '0' - bit is cleared

#### REG\_5 - 'Interrupt RX-FIFO Threshold 1' (Address 0x05) (SPI & I<sup>2</sup>C Only) 5.6

| Bit 7  | Bit 6   | Bit 5   | Bit 4          | Bit 3           | Bit 2   | Bit 1   | Bit 0   |

|--------|---------|---------|----------------|-----------------|---------|---------|---------|

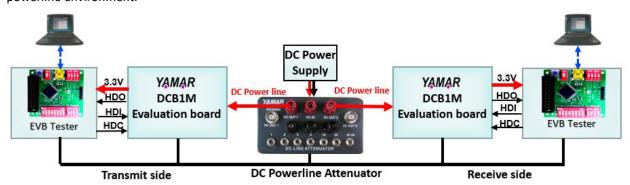

| W/R[0] | R/W [0] | R/W [0] | R/W [0]        | R/W [0]         | R/W [0] | R/W [0] | R/W [0] |