# High Speed Switching Gate Driver

#### ■ GENERAL DESCRIPTION

The NJW4840 is a High Speed Switching Gate Driver that is applicable 4A peak current.

The NJW4840 features are Withstand voltage of 24V, Operating voltage range: 8V to 20V and Fast switching time (27.5ns typical at 4700pF load).

The NJW4840 is suitable for PDP Sustain Pulse Drive, DC / AC Motor Drive, Switching Power Supply, and DC / DC Converter Applications.

## **■ FEATURES**

- Output Peak Current ±4A (peak)

Operating Voltage Range 8V to 20V

- High Speed Switching

27.5nsec(typ.)@CL=4700pF

- Built-in Thermal Shut Down

- Under Voltage Lockout

- Short Circuit Protection (power / ground fault)

- Package MSOP8 (VSP8)

\* MEET JEDEC MO-187-DA

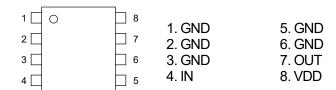

#### ■ PIN CONNECTION

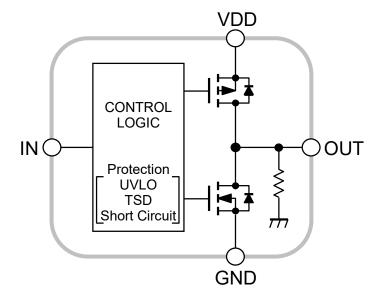

### ■ BLOCK DIAGRAM

#### ■ PACKAGE OUTLINE

# **NJW4840**

# ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYNBOL                | RATINGS               | UNIT | REMARK      |

|-----------------------|-----------------------|-----------------------|------|-------------|

| Supply Voltage        | $V_{DD}$              | +24                   | V    | VDD-GND Pin |

| Input Voltage         | V <sub>IN</sub>       | -0.3 to +6            | V    | IN-GND Pin  |

| Input Voltage (Pulse) | V <sub>IN-pulse</sub> | -0.3 to +7            | V    | IN-GND PIII |

| Power Dissipation     | $P_D$                 | 720 (*1)<br>1100 (*2) | mW   | -           |

| Junction Temperature  | Tj                    | -40 to +150           | °C   | _           |

| Operating Temperature | T <sub>opr</sub>      | -40 to +105           | °C   | _           |

| Storage Temperature   | T <sub>stg</sub>      | -50 to +150           | °C   | _           |

<sup>(\*1):</sup> Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 2Layers)

internal Cu area: 74.2×74.2mm

## ■ RECOMMENDED OPERATING CONDITIONS

(Ta=25°C)

| PARAMETER         | SYMBOL          | MIN. | TYP. | MAX. | UNIT | REMARK      |

|-------------------|-----------------|------|------|------|------|-------------|

| Operating Voltage | $V_{DD}$        | 8.0  | _    | 20   | V    | VDD-GND Pin |

| Input Voltage     | V <sub>IN</sub> | 0    | -    | 5.5  | V    | IN-GND Pin  |

<sup>(\*2):</sup> Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 4Layers),

|                                                |                    |                                                  | ess otherwise noted, V <sub>DD</sub> =16V, Ta=25°C) |           |           |          |  |

|------------------------------------------------|--------------------|--------------------------------------------------|-----------------------------------------------------|-----------|-----------|----------|--|

| PARAMETER                                      | SYMBOL             | TEST CONDITIONS                                  | MIN.                                                | TYP.      | MAX.      | UNIT     |  |

| General                                        |                    |                                                  |                                                     |           |           |          |  |

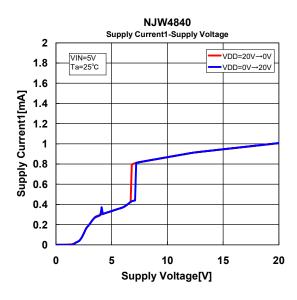

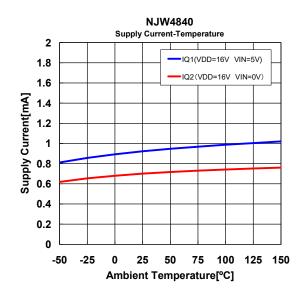

| Quiescent Current                              | I <sub>Q1</sub>    | V <sub>IN</sub> =5V                              | _                                                   | 0.93      | 1.6       | mA       |  |

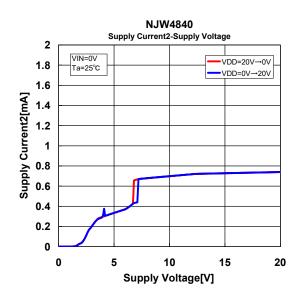

|                                                | I <sub>Q2</sub>    | V <sub>IN</sub> =0V                              | _                                                   | 0.7       | 1.4       | mA       |  |

| Output Block                                   |                    |                                                  |                                                     |           |           |          |  |

| Output Peak Current                            | I <sub>PK1</sub>   | PW≤400ns, V <sub>OUT</sub> =0V                   | _                                                   | 4         | _         | Α        |  |

|                                                | I <sub>PK2</sub>   | PW≤400ns, V <sub>OUT</sub> =16V                  | _                                                   | 4         | _         | Α        |  |

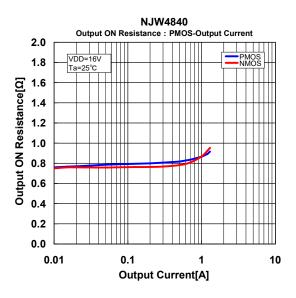

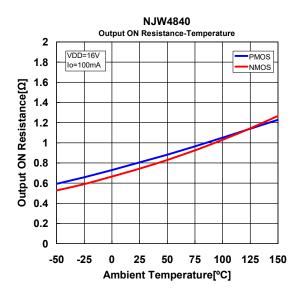

| Output ON Resistance<br>(High-Side / Low-Side) | R <sub>DSH</sub>   | I <sub>O-SOURCE</sub> =100mA                     | _                                                   | 0.8       | 1.5       | Ω        |  |

|                                                | R <sub>DSL</sub>   | I <sub>O-SINK</sub> =100mA                       | _                                                   | 0.8       | 1.5       | Ω        |  |

| Pull Down Resistance                           | R <sub>PD</sub>    |                                                  | 60                                                  | 100       | 140       | kΩ       |  |

| Input Circuit Block                            |                    |                                                  |                                                     |           |           |          |  |

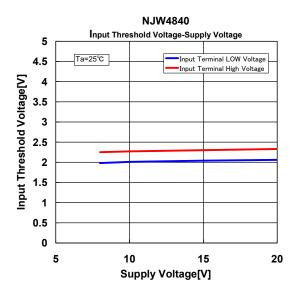

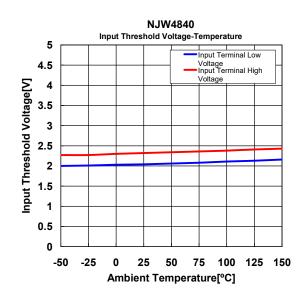

| IN Pin High Resistance                         | V <sub>IHIN</sub>  |                                                  | 3.0                                                 | _         | 5.5       | V        |  |

| IN Pin Low Resistance                          | V <sub>ILIN</sub>  |                                                  | 0                                                   | _         | 1.5       | V        |  |

| IN Pin Sink Current                            | I <sub>IIN</sub>   | V <sub>IN</sub> =5.5V                            | _                                                   | _         | 1         | μΑ       |  |

| IN Pin Hysteresis Voltage                      | $\Delta V_{in}$    | V <sub>IHIN</sub> – V <sub>ILIN</sub>            | _                                                   | 0.3       | _         | V        |  |

| UVLO Block                                     |                    |                                                  |                                                     |           |           |          |  |

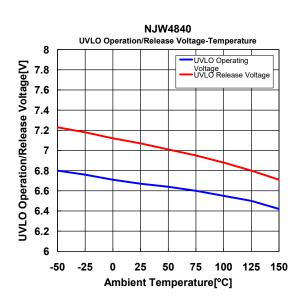

| UVLO Release Voltage                           | $V_{UVLO2}$        |                                                  | 6.3                                                 | 7         | 7.7       | V        |  |

| UVLO Operating Voltage                         | $V_{UVLO1}$        |                                                  | 6                                                   | 6.7       | 7.4       | V        |  |

| UVLO Hysteresis Voltage                        | $\Delta V_{UVLO}$  | V <sub>UVLO2</sub> – V <sub>UVLO1</sub>          | _                                                   | 0.3       | _         | V        |  |

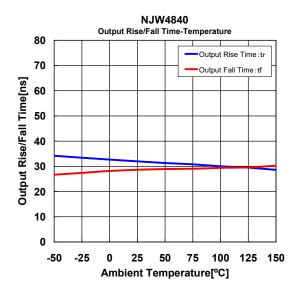

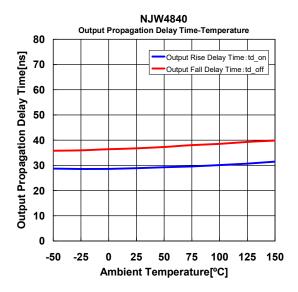

| OUTPUT RISE / FALL CHAR                        | RACTERISTICS       | 3                                                | (V <sub>DD</sub> =16                                | 6V, Ta=25 | °C, Desig | n Value* |  |

| PARAMETER                                      | SYMBOL             | TEST CONDITION                                   | MIN.                                                | TYP.      | MAX.      | UNIT     |  |

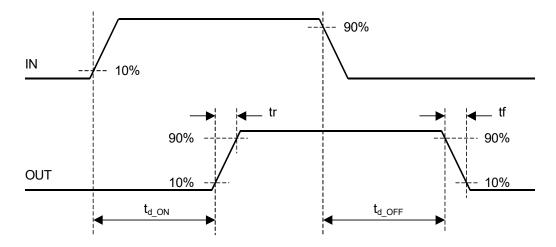

| Output Rise Time                               | tr                 | C <sub>L</sub> =4700pF, V <sub>IN</sub> =0 to 5V | 15.0                                                | 27.5      | 40.0      | ns       |  |

| Output Fall Time                               | tf                 | C <sub>L</sub> =4700pF, V <sub>IN</sub> =5 to 0V | 15.0                                                | 27.5      | 40.0      | ns       |  |

| Rise Delay Time                                | t <sub>d_ON</sub>  | C <sub>L</sub> =4700pF, V <sub>IN</sub> =0 to 5V | 17.5                                                | 30.0      | 42.5      | ns       |  |

| Fall Delay Time                                | t <sub>d OFF</sub> | C <sub>L</sub> =4700pF, V <sub>IN</sub> =5 to 0V | 25.0                                                | 37.5      | 50.0      | ns       |  |

<sup>\*</sup> It is design guaranteed, not tested.

# **NJW4840**

#### **■ TIMING CHART**

#### ■ PROTECTION CIRCUIT OPERATION

Under Voltage Lockout (UVLO)

The VDD pin has UVLO function for malfunction prevention at low voltage condition. When the VDD voltage is less than UVLO Operating Voltage, the output pin is turned off. When the VDD voltage rises to UVLO Release Voltage, normal operation resumes.

### Thermal Shut Down (TSD)

When the junction temperature reaches to 180°C typ., the output pin is turned off. When the junction temperature falls to 170°C typ., normal operation resumes.

## •Short Circuit Protection (power / ground fault)

The OUT pin has current detection circuit for protection against short-circuit to power and ground.

If the output current exceeding the current detection threshold (about 1.4 A) inside the IC continues to flow for more than about 500ns, the output pin is turned off and retained.

This protected state returns to normal operation when the power-on again or the input signal is switched.

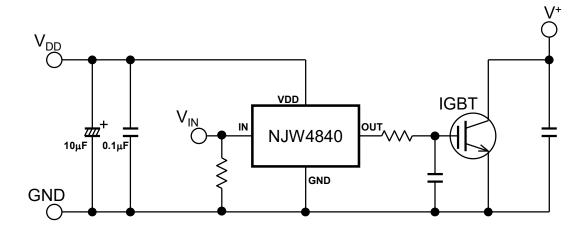

#### ■ TYPICAL APPLICATION

#### ■ APPLICATION TIPS

In the application that does a high-speed switching of NJW4840, because the current flow corresponds to the input frequency, the substrate (PCB) layout becomes an important.

NJW4840 is driving the High-side/Low-side SW gate with high speed to reduce switching losses. The transient voltage is generated by parasitic inductance and a high-speed current change of high side and low side SW.

You should attempt the transition voltage decrease by making a current loop area minimize as much as possible. Therefore, you should make a current flowing line thick and short as much as possible.

You should insert a bypass capacitor between the VDD pin and the GND pin to prevent malfunction by generating over voltage and/or exceed maximum input voltage rating. The recommended bypass capacitor is low ESR and high frequency characteristic (NJR recommends  $0.1\mu F$  or more).

An aluminum electrolysis capacitor is recommended for smoothing condenser. (NJR recommends  $10\mu$ F or more). However, you should use large capacitor by sufficient evaluation (assessment) due to load condition and/or application use environment. (There is a possibility that the supply voltage rises by inductive kickback when the supply current of the inductive load is large.)

The bypass capacitors should be connected as much as possible near the VDD pin.

### ■ TYPICAL CHARACTERISTICS

#### ■ TYPICAL CHARACTERISTICS

[CAUTION]

The specifications on this datasheets are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this datasheets are

described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.